全球电子设计创新的领导者 Cadence Design Systems, Inc. 推出了 Virtuoso,发布版本 ICADVM 20.1 ISR19(20.10.190) 。该软件包含创建 5nm 设计所需的特性和功能,其中包括基于行的加速定制布局和布线方法。

Virtuoso Advanced-Node and Methodology Platform (ICADVM)包含创建 5nm 设计所需的特性和功能,其中包括加速的、基于行的自定义布局和布线方法,使用户能够提高生产力并更好地管理复杂的设计规则。Cadence 推出了支持 5nm 工艺的多项功能,包括堆叠栅极支持、通用多晶硅网格捕捉、基于区域的规则支持、不对称着色和电压相关规则支持、模拟单元支持以及对各种新设备的支持以及属于 5nm 的设计约束台积电的 5nm 技术产品。

安装激活教程参考:《CentOS Linux服务器上Cadence Virtuoso IC618安装教程》

安装说明

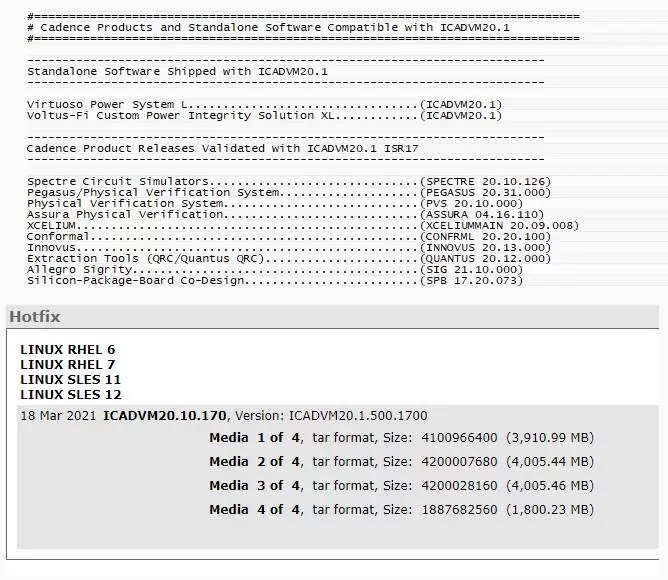

此版本为热补丁,非完整安装版,需要先安装网盘里面的基础版:20.10.000 Base

功能增强

以下列出了对 ICADVM20.1 和 IC6.1.8 ISR14 版本所做的一些重要更新:

ICADVM20.1更新

- 跨结构 EM 模型中的键合线(Virtuoso RF 解决方案)

用于跨结构设计的电磁仿真现在支持通过键合线连接的 IC。 - EM 模拟中的材料文件(Virtuoso RF 解决方案)

在电磁解算器助手发送到 Clarity 3D 进行模拟的过程叠加中指定材料文件。该文件提供对高级材料属性和频率相关电介质的支持。 - 创建拆分符号 (Virtuoso Schematic Editor XL)

使用 Virtuoso Schematic Editor 中的拆分符号功能将一个大符号拆分为多个部分符号。拆分大型符号母版可提高引脚符号的易读性,尤其是在大型 PCB 和封装原理图中。 - 用于静态电源验证的 Virtuoso 电源管理器 (Virtuoso Schematic Editor XL)

Virtuoso 电源管理器通过检查、提取、导出和验证 IP 设计的电源意图来实现模拟和混合信号 IP 的静态电源验证。 - 并发布局中的基于层的流程(Virtuoso Layout Suite EXL 和 Virtuoso Layout Suite XL)

使用并发布局中的基于层的流程定义基于层的分区。定义这些设计分区后,还会创建两个专用约束组。这些约束组可帮助您进行布线和交互式导线编辑。这样,您可以将编辑限制在当前基于图层的设计分区中的那些图层。 - 设计规划和分析(Virtuoso Layout Suite EXL)

Virtuoso Design Planner 工具已被 Virtuoso 设计规划和分析 (DPA) 工具取代,该工具支持更广泛的平面规划、设计规划和拥塞分析功能,包括对硬块、软块和虚拟层次结构的支持。可以通过统一的计划菜单、设计计划工作区和设计计划工具栏访问这种增强的支持,所有这些都可以从 Layout EXL 窗口中获得。

ICADVM20.1 和 IC6.1.8 ISR14更新

- 分发模拟作业(Virtuoso ADE Explorer 和 Virtuoso ADE Assembler)

使用 Virtuoso ADE Explorer 和 Virtuoso ADE Assembler中的默认作业控制模式 LSCS(大规模云模拟)并行控制数千个网表和模拟作业。LSCS 实施了一种新架构,以更好地利用资源运行模拟。它还支持未来对云模拟的可扩展性要求。 - 合并历史 (Virtuoso ADE Assembler)

将多个历史的结果合并到一个历史中,而无需运行模拟。合并历史不仅可以合并来自不同历史的结果,还可以合并这些历史中使用的设置。 - 性能诊断工具(Virtuoso 设计环境)

使用性能诊断工具来隔离可能导致应用程序减速或冻结的问题。它有一个自动隐藏的控制工具栏,让您在应用程序变慢时记录调用堆栈。

软件介绍

Cadence Virtuoso 系统设计平台 链接了两种世界一流的 Cadence 技术——定制 IC 设计和封装/PCB 设计/分析——创建了一种整体方法,可以自动化和简化多芯片异构系统的设计和验证流程。

利用 Virtuoso 原理图编辑器和 Virtuoso 模拟设计环境,它为 IC 和封装/系统级设计捕获、分析和验证提供了一个单一平台。此外,Virtuoso 系统设计平台提供与 Cadence SiP 级实施环境和 Clarity 3d Solver 的自动双向接口。

Virtuoso 系统设计平台使 IC 设计人员能够轻松地将系统级布局寄生参数包含在 IC 验证流程中,通过将封装/电路板布局连接数据与 IC 布局寄生电气模型相结合来节省时间。自动生成的“系统感知”原理图可以轻松用于创建最终电路级仿真的测试平台。Virtuoso 系统设计平台使整个流程自动化,消除了将系统级布局寄生模型集成回 IC 设计人员流程的高度手动且容易出错的过程。

Product: Cadence Virtuoso ICADVM

Version: 20.1 ISR19 (20.10.190) 热补丁

Supported Architectures: lnx86

Website Home Page : http://www.cadence.com

Languages Supported: english

System Requirements: Linux *

Size: 10.3 Gb