半导体设计软件的全球领导者 Synopsys, Inc. 推出了 Synopsys SpyGlass vQ-2020.03 SP2-3——早期设计分析工具可实现 FPGA 设计的高效静态验证。

Synopsys FPGA设计解决方案包括高质量、高性能和易于使用的 FPGA 实施、验证和调试工具。使用 Synopsys FPGA 设计工具的设计人员可以快速获得复杂 FPGA 的结果、降低成本和功耗的面积优化、领先的 HDL 语言支持,以及加快 FPGA 设计开发的增量和团队设计能力。Synopsys FPGA 设计工具通过提供 DesignWare IP 集成、使用 VCS 的高性能功能验证链接、用于时钟域交叉分析的静态验证和使用 SpyGlass 的 lint、与 Synphony Model Compiler 的集成以及用于 FPGA 的 ASIC 兼容综合流程来提供附加价值- 基于原型。

SpyGlass平台在 RTL 流程的早期阶段,使用许多先进的算法和分析技术为设计人员提供有关其设计的洞察力。SpyGlass 的功能类似于设计工程师和管理人员的交互式指导系统,为具有内部和第三方 IP 的复杂 FPGA 找到最快、最便宜的实施途径。SpyGlass Lint 和 CDC 提供静态验证解决方案,以解决与 RTL 编码最佳实践、设计可重用性和多个异步时钟域交叉 (CDC) 相关的问题,例如亚稳态、数据重新收敛、FIFO 完整性等。

Product: Synopsys SpyGlass

Version: vQ-2020.03 SP2-3 *

Supported Architectures: x86_x64

Website Home Page : http://www.synopsys.com

Languages Supported: english

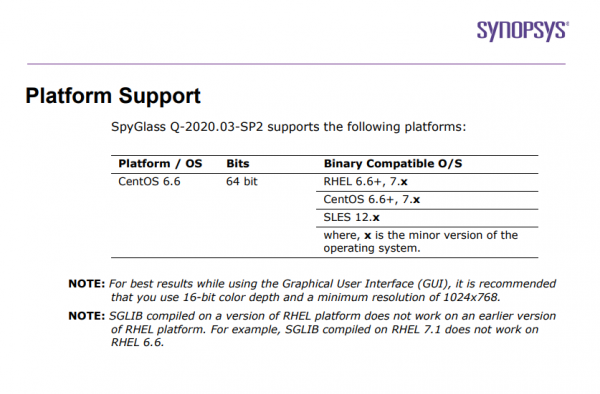

System Requirements: Linux **

Size: 16.0 Gb

* release info: spyglass_vQ-2020.03-SP2-3_common.spf

spyglass_vQ-2020.03-SP2-3_docs.tar.gz

ufe_optional_spyglass-vcs_vQ-2020.03-SP2-3_common.spf

ufe_optional_spyglass-vcs_vQ-2020.03-SP2-3_common.spf.csh

ufe_optional_spyglass-vcs_vQ-2020.03-SP2-3_common.spf.part00

ufe_optional_spyglass-vcs_vQ-2020.03-SP2-3_common.spf.part01

ufe_optional_spyglass-vcs_vQ-2020.03-SP2-3_common.spf.part02

ufe_optional_spyglass-vcs_vQ-2020.03-SP2-3_common.spf.part03

ufe_optional_spyglass-vcs_vQ-2020.03-SP2-3_common.spf.README

spyglass_INSTALL_README.txt