Xilinx, Inc. 是自适应和智能计算领域的领导者,很高兴地宣布 Xilinx Vivado Design Suite 2022.1 的面市,这是一个用于其 FPGA 和 SoC 系列的 HDL 设计、综合和分析的软件套件。Vivado Design Suite 包含许多工具,例如 Vivado、Vitis、Vitis HLS 等。

2022.1新版新增功能

Versal QoR 改进

– 根据默认或探索策略快 5-8%

基于 ML 的资源估计

——为 IP 提供实时资源估计数据

ML Strategy Runs 现在可用于 Versal 设备

– 在迭代难以满足时序的设计时很有用

EA 功能

– 对 Versal 设备的抽象 Shell 支持

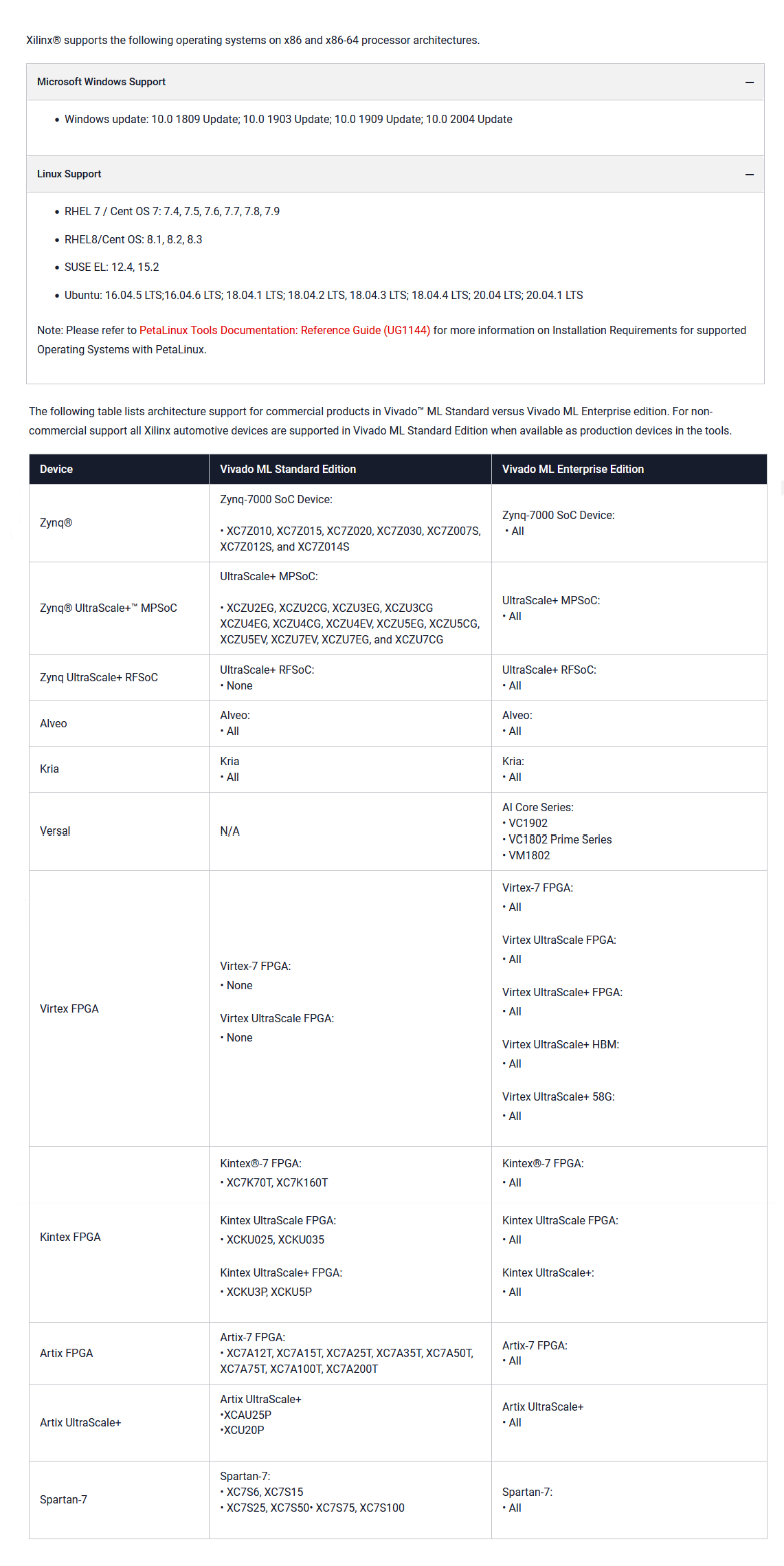

Vivado ML 企业版和标准版中启用的器件

– Artix UltraScale+ 器件:XCAU15P 和 XCAU10P

– 其他 Versal Prime、Premium、AI Core 和 AI Edge 系列器件

Vivado Design Suite是Xilinx为HDL设计的综合和分析而设计的软件套件,取代了Xilinx ISE,具有用于片上系统和高级综合的附加功能。 Vivado代表了对整个设计流程的重新思考和重新思考,并且被评论者描述为“精心构思,紧密集成,快速,可扩展,可维护和直观”。

Vivado Design Suite提供了多种方法来完成 Xilinx FPGA 设计和验证所涉及的任务。除了传统的 RTL 到比特流 FPGA 设计流程之外,Vivado 设计套件还提供了专注于以 IP 为中心的设计的新系统级集成流程。在流程的每个阶段都启用设计分析和验证。设计分析功能包括逻辑仿真、I/O 和时钟规划、功耗分析、时序分析、设计规则检查 (DRC)、设计逻辑和实现结果的可视化以及编程和调试。

整个解决方案集成在称为 Vivado 集成设计环境 (IDE) 的图形用户界面 (GUI) 中。Vivado IDE 提供了一个接口来组装、实施和验证设计和 IP。此外,所有流程都可以使用 Tcl 应用程序编程接口 (API) 运行。Tcl 命令可以使用 Tcl 提示以交互方式输入或保存在 Tcl 脚本中。您可以使用 Tcl 脚本运行整个设计流程,包括设计分析,或者只运行部分流程

加速智能系统的开发需要超越 RTL 级别设计的自动化级别。随着 Vivado 设计套件的推出,Xilinx 提供了一个以 SoC 为核心、以 IP 和系统为中心的下一代开发环境,该环境从头开始构建,以解决系统级集成和实施中的生产力瓶颈

Xilinx 开发高度灵活和自适应处理平台,可实现从端点到边缘再到云的各种技术的快速创新。Xilinx 是 FPGA、硬件可编程 SoC 和 ACAP 的发明者,旨在提供业内最具动态性的处理器技术,实现未来的适应性、智能和互联世界。

Xilinx 现在是 AMD 的一部分。 AMD 现在拥有业界最广泛的产品组合和高度互补的技术集,可覆盖不同市场的客户。AMD 和 Xilinx 携手为正确的工作负载利用正确的引擎来满足我们客户的计算需求。

Product: Xilinx Vivado Design Suite

Version: 2022.1_0420_0327 (Unified Installer) *

Supported Architectures: x86 and x86-64

Website Home Page : http://www.xilinx.com

Languages Supported: english

System Requirements: Linux **

Size: 77.9 Gb

* Important Information

The Xilinx Unified Web Installer supports the feature to download full image containing all devices and tool options without running installation.

The Xilinx Unified Web Installer also allows you to download only what you need! Use this option to select and install your desired Xilinx Tools:

– Vivado ML Edition

– Vitis

– Petalinux

– On-premise Install for Cloud Deployment

– Bootgen

– Lab Edition

– Hardware Server